增量式光电编码器|设计增量式编码器的接口电路( 二 )

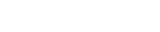

从图4中虚线所示的状态可知,A1和A2,B1和B2两组信号里都有一组不同的电平状态,故采用3个异或门以求得信号的4倍频信号F百思特网4_CLK 。与此同时,采用两个与非门来求得方向信号 。

图4 A、B信号经D触发器后的信号图

光电编码器线数为1024,四倍频后旋转一圈产生4096个脉冲,其精度为0.0879o 。为满足精度要求,本设计采用的是16位可逆计数器,计数范围为-65536~65535,利用Altera公司的设计软件自带的LPM(宏功能模块)模块实现该计数模块 。

接口电路的设计与实现本设计使用的软件是Altera公司的Quartus II,选用的芯片是CycloneⅢ的EP3C16Q240 。该芯片有15408个逻辑单元,56个乘法器,4个锁相环,20个全局时钟网络,存储器容量为504Kbit,最高工频率可为437.5MHz,输入输出电压3.3V[8],如此强大的资源足以实现设计预期的功能 。

1 子模块的原理图设计

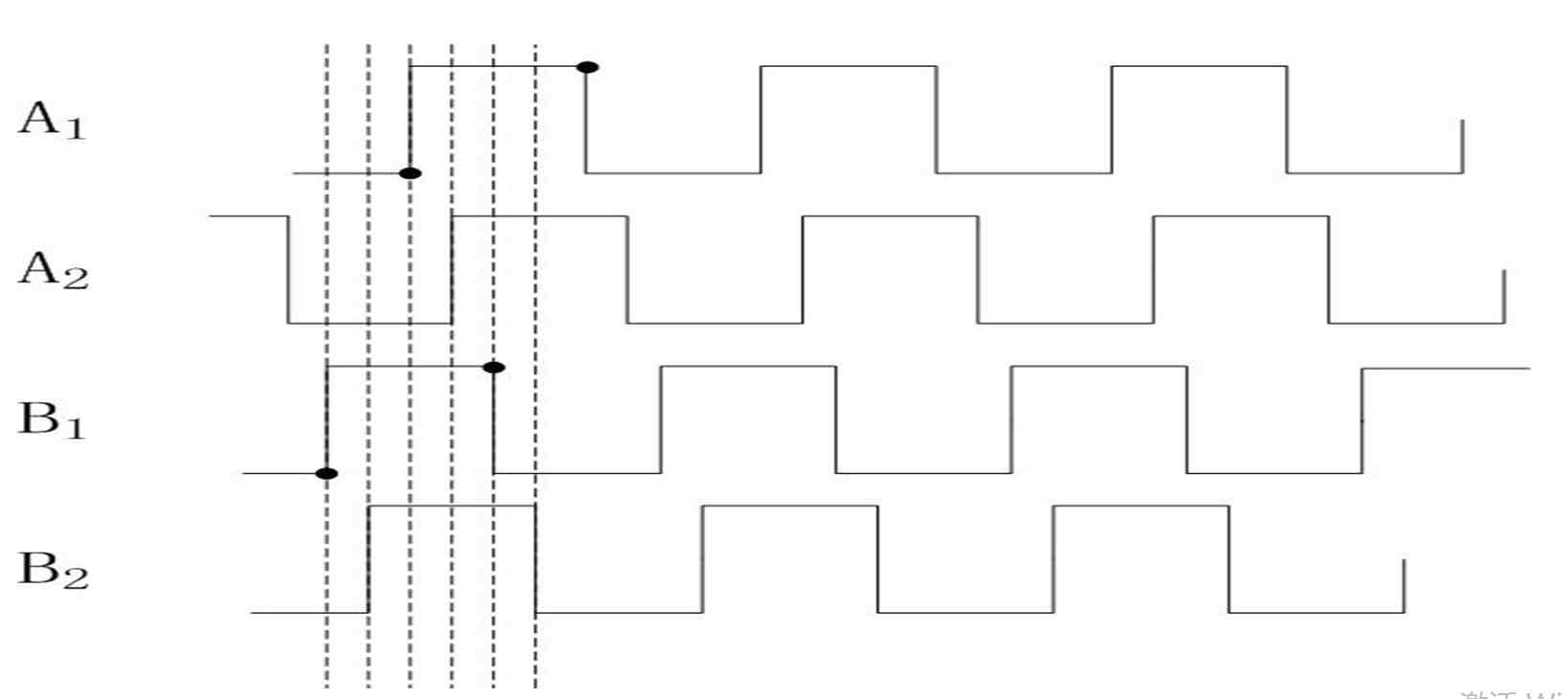

FPGA具有动态可系统重构和静态可重复编程的特性,使得可以像软件一样通过编程来修改硬件的功能 。我们可以通过原理图输入或者HDL(硬件描述语言)来设计实现一个数字系统 。根据上一节原理的介绍,生成倍频、鉴相、计数模块的顶层文件原理图,如图5所示 。

图5 顶层原理图

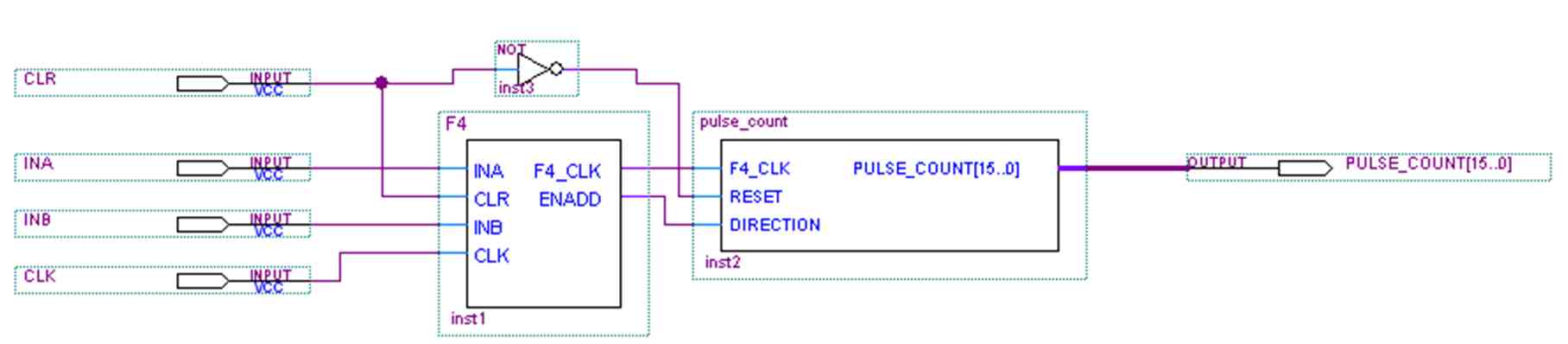

其中,输入为正交编码信号A、B,输出为16位计数结果百思特网 。该顶层原理图分为两部分,一个是倍频、鉴相模块,如图6所示;一个是使用自带的宏功能模块实现的计数模块 。编码信号经倍频、鉴相后产生四倍频信号F4_CLK、方向信号ENADD,再经过pluse_count实现16位百思特网可逆计数功能 。当ENADD为高电平即码盘正转时,实现加法计数;当ENADD为低电平即码盘反转时,实现减法计数 。

图6 倍频、鉴相原理图

2 编译及下载

在Quartus II中依次进行如下操作:新建工程、选择目标芯片、绘制原理图、管脚分配、芯片参数及配置选项设置,即可对设计文件进行编译 。

编译完成后将在工程文件夹下将生成后缀名为sof和pof的两个下载文件,这两个文件的区别在于:前者是通过JTAG口下载到FPGA芯片中(配置FPGA芯片),直接运行程序,而掉电后程序消失;后者是通过AS口下载到配置芯片中,上电后将自动完成配置,运行程序 。

前者下载的速度快,一般用于FPGA的调试过程;而后者由于是烧写EPCS配置芯片(实际上是串行FLASH),速度较慢,一般用于开发后期的程序固化 。本次设计也是遵循调试阶段采用JTAG模式烧写下载,待程序确定后采用AS模式烧写下载[11] 。

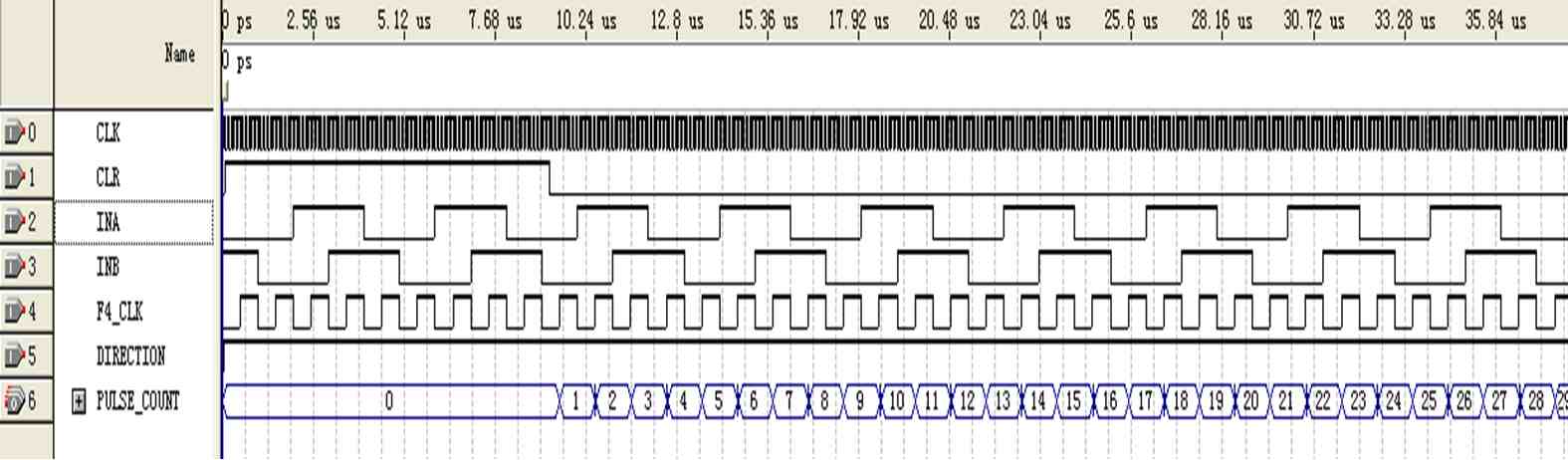

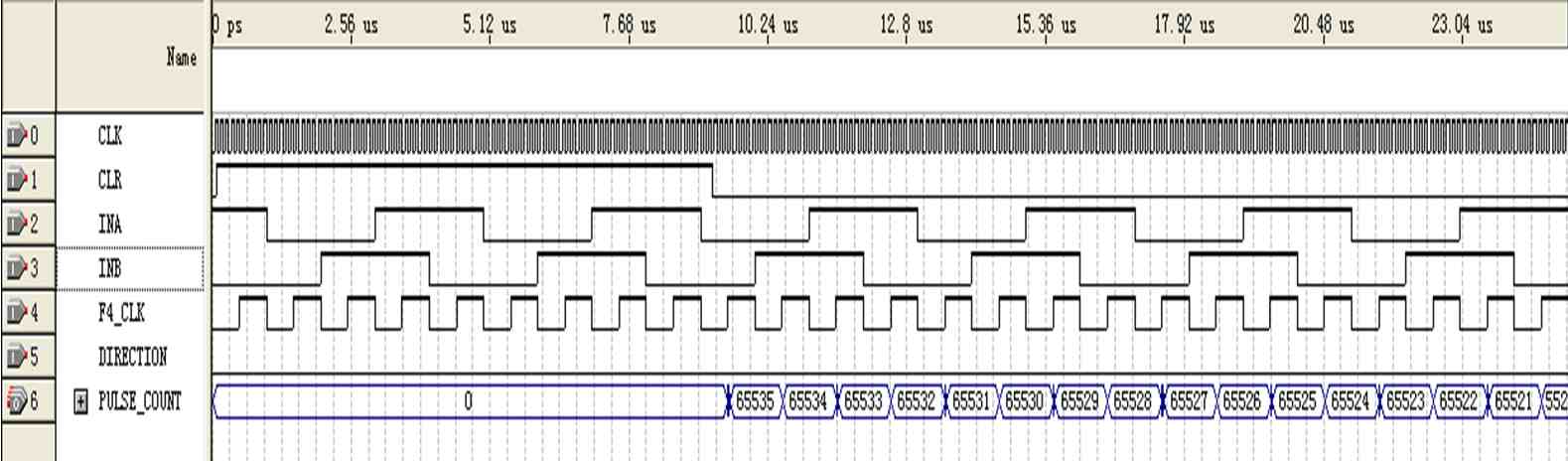

波形仿真及分析编译通过后,我们使用Quartus II自带的仿真器进行功能仿真以验证设计的逻辑是否正确 。在建立矢量源文件时,首先设置编码信号A超前B 90o得到仿真结果如图7所示;然后设置编码信号B超前A 90o得到仿真结果如图8所示 。

从图7、图8中可以看出,当信号A超前B 90o即电机正转时,方向信号为高电平,实现四倍频且一个周期内加法计数4次;反之,当信号B超前A 90o即电机反转时,方向信号为低电平,同样实现四倍频且一个周期内减法计数4次 。由此可知,仿真结果与理论分析完全一致,本接口电路逻辑正确,具有实际意义 。

在实际调试阶段中,连接好编码器和电路板,通过QuartusII的Signaltap II来捕捉和显示实时信号,所得的结果与预期也是一致的,从而进一步验证了设计的可靠性 。

图7 信号A超前B 90o仿真结果

图8 信号B超前A 90o仿真结果

小结基于FPGA的增量式编码器的接口设计实现了对编码信号数据的采集和处理,克服了使用ASIC(专用集成电路)对数据进行处理而产生的编译复杂、通用性差等缺点 。该接口电路具有适用性好、集成度高、抗干扰性强、运行可靠、数据处理快等优点,适用于各种需要使用增量式编码器测量位置和速度的场合 。

- 求婚|七夕求婚方式排行榜,七夕有哪些浪漫的求婚方式

- 结婚|结婚三金可以换别的款式吗

- 黄金|什么款式的黄金手镯容易磨损

- 后半生最舒服的生活方式(深度好文)

- 遇事最高明的处理方式:面缓、声静、心安

- 人与人之间最大的差距:思维模式

- 德祐的门店复制模式——如何快速培养人才? 薄荷曼哥

- 榻榻米床|怎么拆榻榻米床

- 三大人际关系公式,记住终生受益

- 住宅|住宅式公寓适合长期居住吗